## MS89F/L 09Series

## 8051 High Speed Flash CPU With ADC

### Hardware SPEC

**MSHINE Technologies Corporation**

HEAD QUARTER

TEL: +886-3-5833899 FAX: +886-3-5830858

SHENZHEN OFFICE

TEL:+86-755-88250870 FAX:+86-755-88250872

### Contents

| CONTENTS                                                           | 2  |

|--------------------------------------------------------------------|----|

| FIGURES                                                            | 5  |

| TABLES                                                             | 6  |

| FEATURES                                                           |    |

| BLOCK DIAGRAM                                                      |    |

|                                                                    |    |

| PRODUCTS                                                           |    |

| PACKAGE                                                            | 9  |

| GENERAL DESCRIPTION                                                | 9  |

| DOCUMENT CHANGE HISTORY                                            | 9  |

| PINS CONFIGURATION                                                 | 10 |

| PIN DESCRIPTIONS                                                   | 12 |

| ABSOLUTE MAXIMUM RATINGS                                           | 14 |

| 8052 COMPATIBLE CPU CORE                                           | 14 |

| CPU Architecture                                                   |    |

| Memory Types                                                       |    |

| 8052 Compatible Special Function Registers (SFR)                   |    |

| <i>I/O Registers</i>                                               |    |

| Register Banks                                                     |    |

| Accumulator (ACC)                                                  |    |

| Program Status Word (PSW)                                          |    |

| Program Counter (PC)                                               |    |

| Stack Pointer (SP)                                                 |    |

| Data Pointer (DPTR)                                                |    |

| Interrupt Registers                                                |    |

| Timer Registers                                                    |    |

| Serial Control Registers                                           |    |

| B Register                                                         |    |

| PCON Register                                                      |    |

| Non-compatible Functions and Registers                             |    |

| Standard 8052 Addressing Modes<br>Implied Register Addressing Mode |    |

| Bit Addressing Mode                                                |    |

| Immediate Addressing Mode                                          |    |

| Direct Addressing Mode                                             |    |

| Indexed (Indirect) Addressing Mode                                 |    |

| MSHINE 8052 Instruction Execution                                  |    |

| MS81/MS89 SERIES MEMORY MAP                                        | 18 |

| SFR Registers                                                      | 19 |

| Direct Addressing Mode registers                                   |    |

| XMEM Addressing Mode registers                                     |    |

| INTERRUPTS                                                         |    |

| Interrupt Vectors                                                  |    |

| Interrupt Priority                                                 |    |

| Interrupt Masking                                                  |    |

| SYSTEM RESET                                                       |    |

|                                                                    |    |

| CLOCK DISTRIBUTION                                                 |    |

| POWER CONTROL MODES                                 |    |

|-----------------------------------------------------|----|

| IDLE Mode                                           |    |

| Power-Down Mode                                     |    |

| Wake-Up Sources                                     |    |

|                                                     |    |

| LOW VOLTAGE STOP/DETECT                             |    |

| I/O PORTS                                           |    |

| Port 0                                              |    |

| Port 1                                              |    |

| Port 3                                              |    |

| I/O Pin Interrupts<br>CMOS I/O                      |    |

| TIMERS                                              |    |

| Timer 0 and Timer 1                                 |    |

| Timer 2                                             |    |

| WATCH-DOG TIMER                                     |    |

| SERIAL INTERFACE - UART                             |    |

| Receiving Data when RI is 1                         |    |

| PFD (PROGRAMMABLE FREQUENCY DIVIDER)                |    |

|                                                     |    |

| PULSE WIDTH MODULATION (PWM)                        |    |

| PWM Duty with PWTH SFR                              |    |

| ANALOG TO DIGITAL CONVERTER (ADC)                   |    |

| ADC Program Example                                 |    |

| SPI                                                 |    |

| SPI Master Program Example                          |    |

| SPI Slave Program Example                           |    |

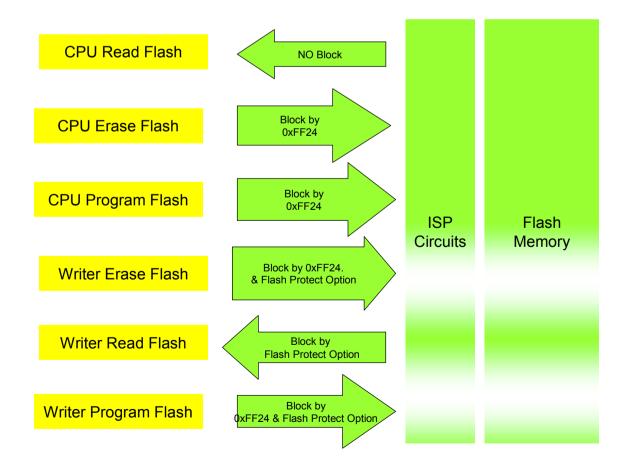

| I2C                                                 |    |

| I2C Slave Addresses                                 |    |

| I2C Slave Clock Stretching                          |    |

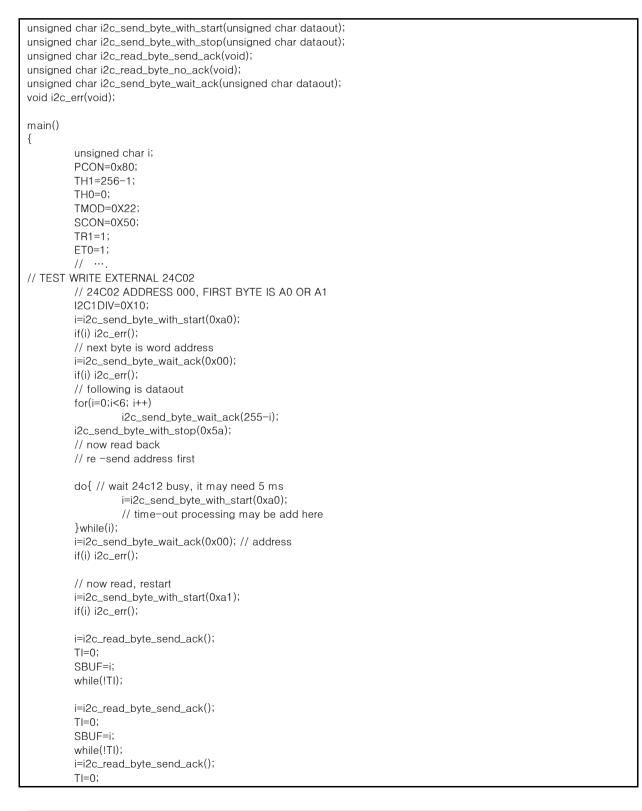

| I2C Control Registers<br>I2C Master Example Program |    |

| I2C Master Example Program                          |    |

| I2C Timing Diagram                                  |    |

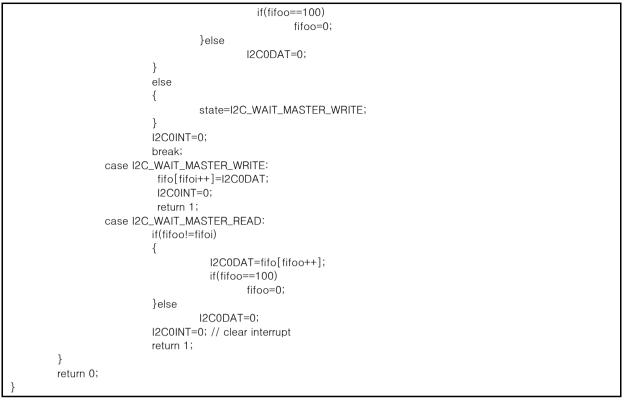

| Extern Master Writes MS89XX                         |    |

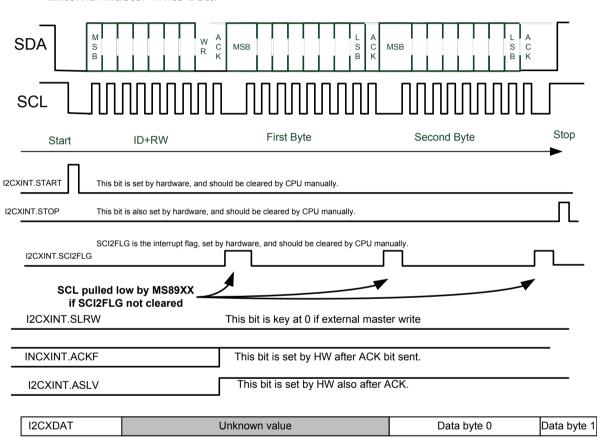

| External Master Read MS89XX                         |    |

| External Master Read/Write Other Device             |    |

| IN APPLICATION PROGRAMMING (IAP)                    |    |

| Programmed by CPU Itself                            |    |

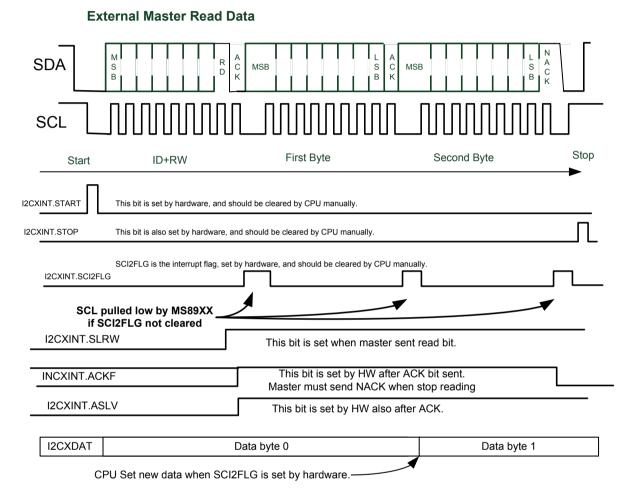

| Sector Erasing/Programming<br>Flash Data Protection |    |

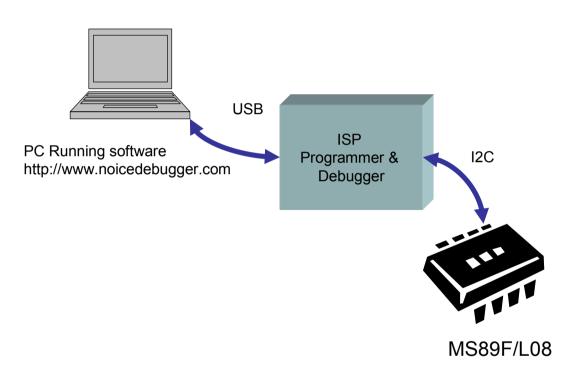

| IN SYSTEM DEBUGGER                                  |    |

|                                                     |    |

| FLASH INFO SECTOR                                   |    |

| AC & DC ELECTRICAL CHARACTERISTICS                  |    |

| DC Characteristics – I/O, CPU                       |    |

| AC Electrical Characteristics – Oscillators         |    |

| AC ELECTRICAL CHARACTERISTICS – ADC                 |    |

| DC Characteristics - ADC                            | 99 |

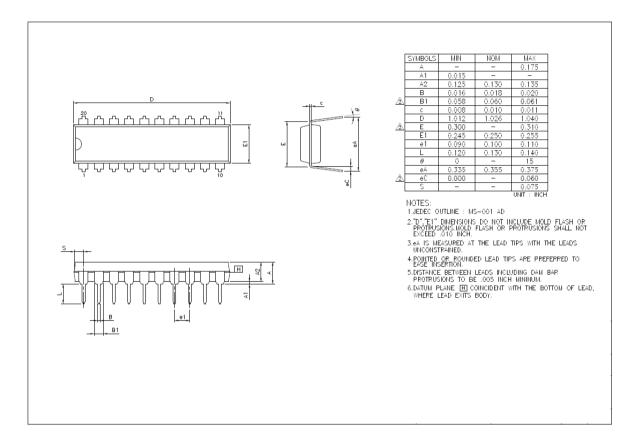

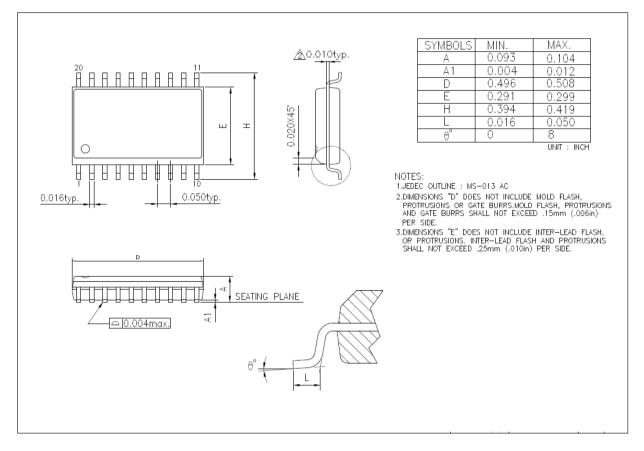

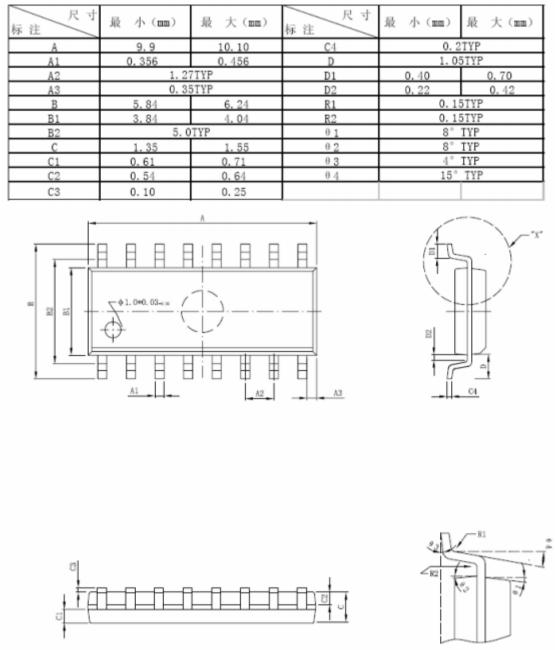

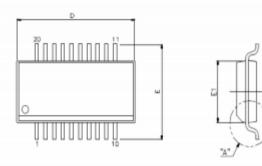

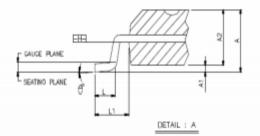

| PRODUCT PROCUREMENT |  |

|---------------------|--|

| PACKAGE SIZE        |  |

| DIP20               |  |

| SOP20               |  |

| SOP16               |  |

| SSOP                |  |

### Figures

| -igure 1. MS89F/L series Block Diagram                   | 8  |

|----------------------------------------------------------|----|

| igure 2. Pins Configuration                              | 11 |

| igure 3. MSHINE 8051 Core structure                      | 15 |

| igure 4. Memory Map                                      | 19 |

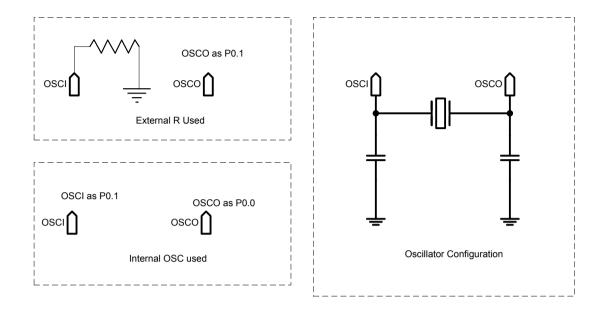

| igure 5. Oscillator Source                               | 37 |

| igure 6. Clock Hardware configuration                    | 40 |

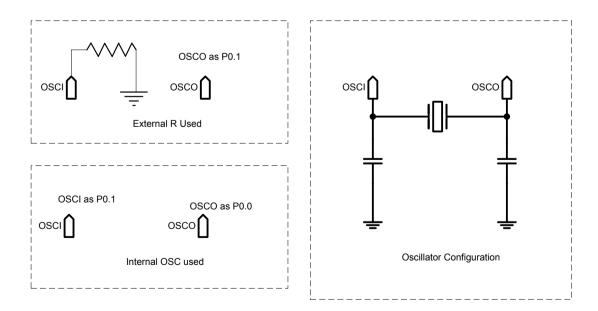

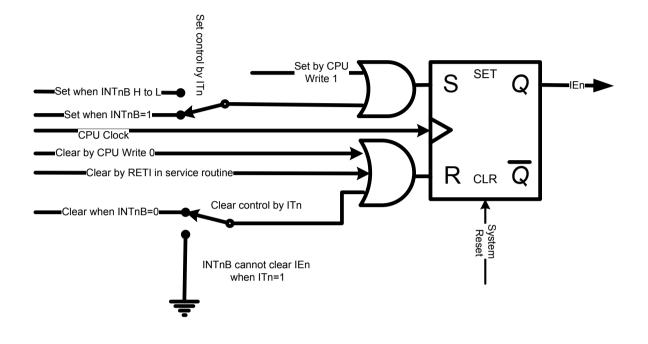

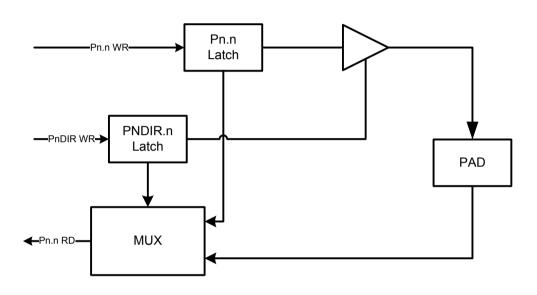

| igure 7. Port configuration                              | 42 |

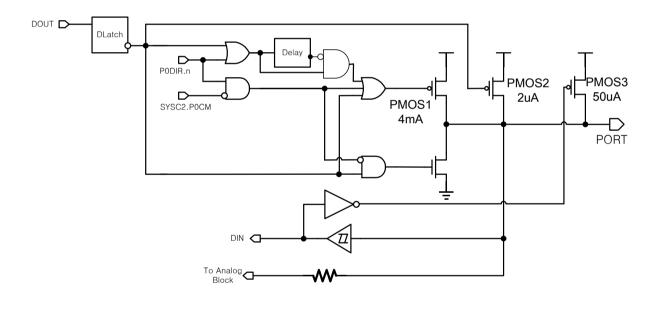

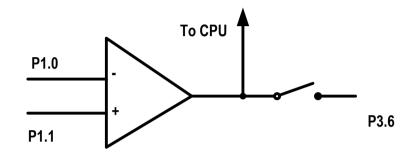

| igure 8. IE0/IE1 Concept Diagram                         | 44 |

| Figure 9. MS89F/L SERIES CMOS I/O                        | 45 |

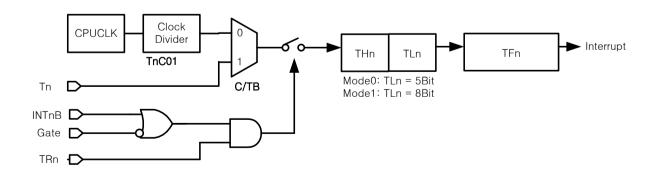

| igure 10. Timer 0 and Timer 1 Mode 0 and 1 configuration | 47 |

| igure 11. Timer 0 and Timer 1 Mode 2, auto reload mode   | 48 |

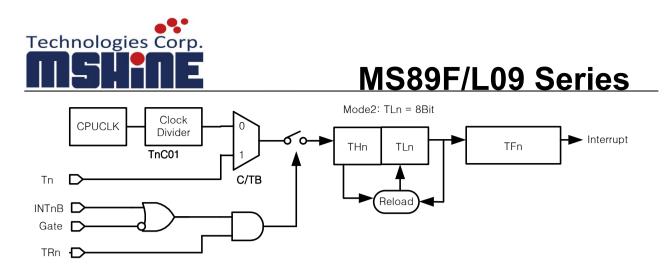

| igure 12. Timer 0 Mode 3                                 | 48 |

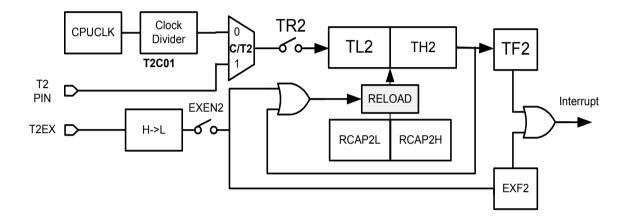

| igure 13. Timer 2 in auto-reload mode                    | 49 |

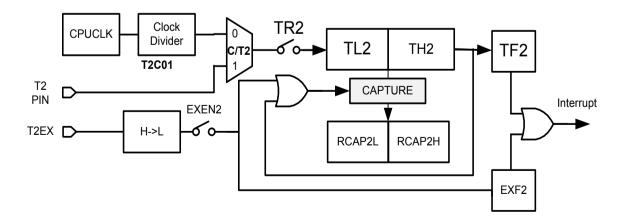

| igure 14. T2 in capture mode                             | 49 |

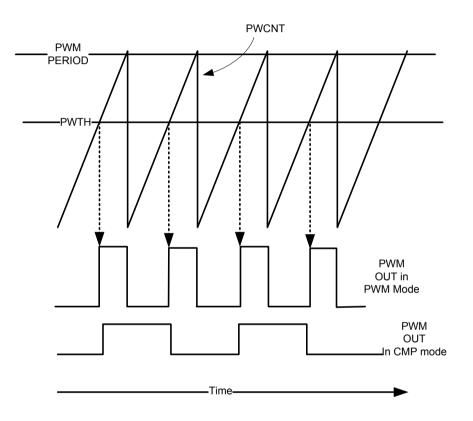

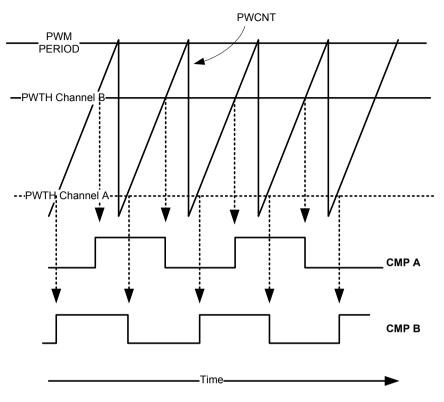

| igure 16. PWM Generation principle                       | 57 |

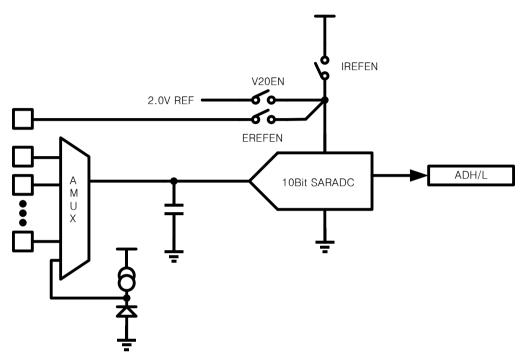

| igure 17. ADC and Reference Configuration                | 63 |

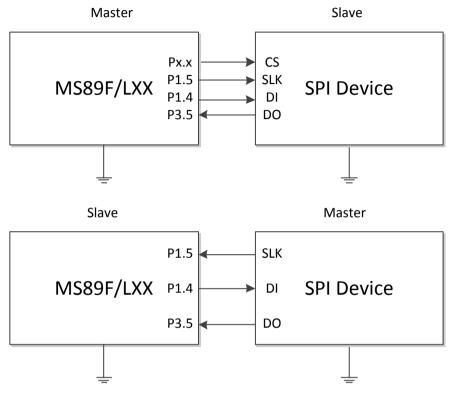

| igure 18. MS89F/L SERIES SPI Configuration               | 71 |

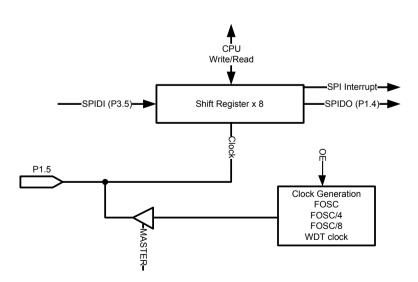

| igure 19. SPI Configuration                              | 71 |

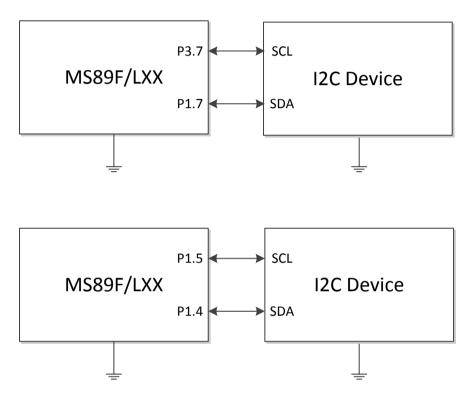

| igure 20. MS89F/L SERIES I2C Configuration               | 77 |

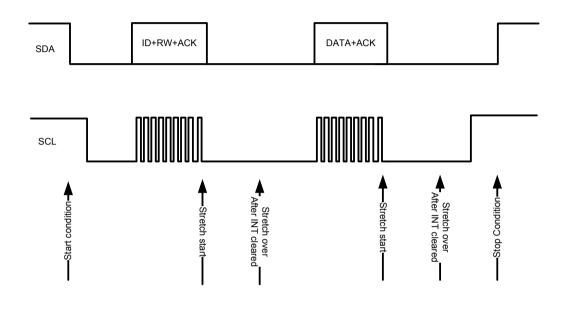

| igure 21. I2C Slave SCL Stretching                       | 78 |

| igure 22. External Master Writes MS89XX                  | 87 |

| igure 23. External Master Reads MS89XX                   | 88 |

| igure 24. Flash Protection Scheme                        | 92 |

| igure 25. MS89FXX In System Debugger Configuration       | 93 |

| igure 26. In System Debugger used recources              | 94 |

### Tables

| Table 1. | MS89F/L series DIP/SOP20 Pins Configuration | 11  |

|----------|---------------------------------------------|-----|

| Table 2. | MS89F/L SERIES Pins Description.            | 13  |

| Table 3. | Port 1 multi-functions                      | 43  |

| Table 4. | Port 3 multi-functions                      | 43  |

| Table 5. | DC Characteristics - I/O, CPU               | 98  |

| Table 6. | AC Electrical Characteristics - Oscillators | 98  |

| Table 7. | AC Characteristics - ADC                    | 99  |

| Table 8. | ADC DC characteristics                      | 99  |

| Table 9. | Product procurement                         | 100 |

### Features

- 8-bit High Speed micro-controller built in

- <u>8K</u> bytes Flash Memory

- In Application Programming (IAP) support.

- 4x2K bytes sectors can be erased or programmed independently.

- Program code can be protected by hardware.

- CPU can upgrade FLASH by running programs in RAM.

- Total 512 bytes RAM. 256 bytes Internal DATA RAM (Random Access Memory), (IRAM). 256 Byes external RAM (XRAM). XRAM can be switched to Program area.

- Three selectable clock source for CPU:

\* External Oscillator (Up to 20MHz)

\* RC oscillator with external R (up to 20MHz)

- \* Internal trimmed Oscillator 8MHz at 3.3V/5V).

- Maximum 18 Programmable I/O pins. (P0 ~ P3)

- 3 timers built in, compatible to Intel 80C32.

Also an additional watch-dog timer to prevent system halt.

- Watchdog timer uses independent low speed internal low power oscillator that can be used as low power "wakeup" interrupt source.

- 10-bit ADC built in, with 16 selectable input sources.

- ADC can use internal regulated reference or external reference.

- Analog Comparator built in.

- Standard UART interface. With 11.059 MHZ Oscillator, the baud rate may be exact 115200 BPS.<sup>1</sup>

- TWO I2C Ports master/slave.

- One SPI Master/Slave Port.

- 3 Ch 10-bits PWM/CMP output pins.

PWM can set change both period and duty.

- 5 interrupt input sources shared with I/O port.

- Low Voltage Stop/ Detect capability

- Low Voltage Reset

- APOR : Power on reset .

- PFD : Programmable Frequency Divider Output.

- Hardware Watch Dog Timer.

- Standby mode, Stop mode

- MS89F series Operating voltage range: 4.5V ~ 5.5V.

- MS89L series Operating voltage range: 2.4V ~ 3.6V.

<sup>&</sup>lt;sup>1</sup> For UART using IRC at 115200 BPS, please contact MSHINE.

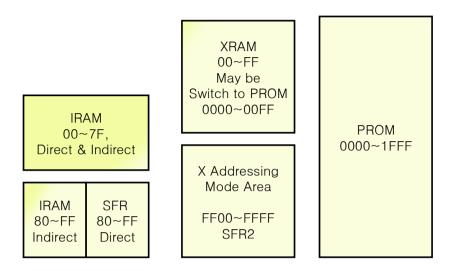

Block Diagram

| Regulator       | 1T 80       | •             |            | RESET                |                    |

|-----------------|-------------|---------------|------------|----------------------|--------------------|

| IRC/ERC/OSC     | Co          | re            |            | Watchdog             | P00,P01<br>P10~P17 |

|                 | ]           |               | <b>→</b>   | I/O                  | P30~P37<br>←───    |

| ADCX16          | <b>↓</b>    |               |            | LVD/LVR/             |                    |

| Timerx3         | <b>←</b> →→ |               |            | Comparator           |                    |

| UART            | <b>←</b> →→ | <b>↓</b>      | <b>→</b> [ | ISP/IAP              |                    |

|                 |             | •             | <b>→</b> [ | SPI                  |                    |

| 512 BYTE<br>RAM | ← →         | •             | <b></b>    | 8K FLASH<br>ROM      |                    |

| PFD             | <b>←</b> →→ | <u>ــــــ</u> |            | 124 BYTE<br>DATA ROM |                    |

| PWM<br>CMP X3   | <b>←</b> →  | <br>          |            | I2CX2                |                    |

Figure 1. MS89F/L series Block Diagram.

### Products

| Item        | Operating   | Flash | SRAM           | Data Flash<br>(Option) |         | INFO     | A/D    | Package  |   |       |

|-------------|-------------|-------|----------------|------------------------|---------|----------|--------|----------|---|-------|

| Voltage     | ROM         | Byte  | Program<br>Rom | Data<br>Rom            | Sector  | 10 Bit   |        |          |   |       |

|             | 5.5V ~ 4.5V | 8K    | 512            | 8K, 6K,                | 0K, 2K, | 124 Byte | V      | DIP20    |   |       |

| MS89F/L09   | 3.6V ~ 2.4V | õn    | ON             | ON                     | 512     | 4K, 2K   | 4K, 6K | 124 Dyte | v | SOP20 |

| MS89F/L109  | 5.5V ~ 4.5V | 8K    | 512            | 8K, 6K,                | 0K, 2K, | 124 Byte | V      | DIP16    |   |       |

|             | 3.6V ~ 2.4V | ÖK    | 512            | 4K, 2K                 | 4K, 6K  | 124 Dyte | v      | SOP16    |   |       |

| MS89F/L309  | 5.5V ~ 4.5V | 8K    | 512            | 8K, 6K,                | 0K, 2K, | 124 Byte | V      | DIP 8    |   |       |

| WI30917L309 | 3.6V ~ 2.4V | ON    | 512            | 4K, 2K                 | 4K, 6K  | 124 Dyle | v      | SOP 8    |   |       |

### Package

■ 20, 16, 14, 8 Pin package.

### **General Description**

MS89F/L series is a general purpose microcontroller that is suitable for commercial or industrial applications like charger, industrial control, and other applications.

### Document Change History

V001: First release. V003: Add VREF. V004: I/O modified.

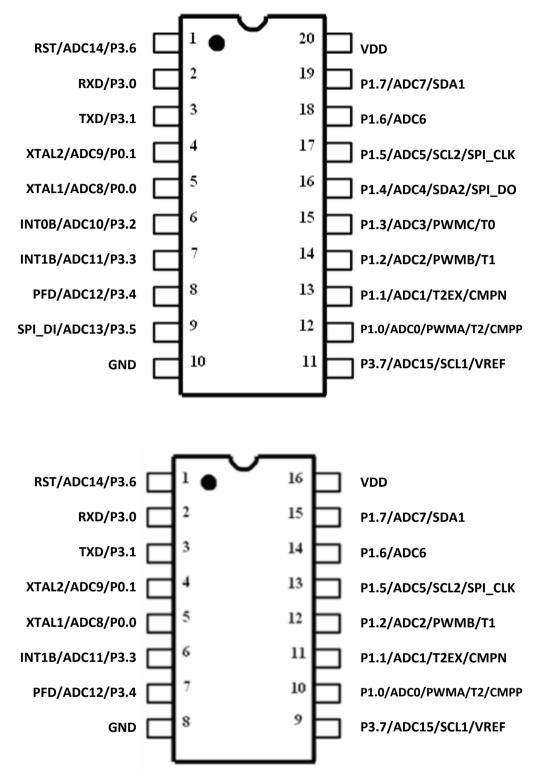

**Pins Configuration**

Figure 2. Pins Configuration

| PIN # | Name              | PIN # | Name                   |

|-------|-------------------|-------|------------------------|

| 1     | RESETB/P3.6/ADC14 | 20    | VDD                    |

| 2     | P3.0/RXD          | 19    | P1.7/SDA1/ADC7         |

| 3     | P3.1/TXD          | 18    | P1.6/ADC6              |

| 4     | XTAL2/P0.1/ADC9   | 17    | P1.5/SCL2/ADC5/SPI_CLK |

| 5     | XTAL1/P0.0/ADC8   | 16    | P1.4/SDA2/ADC4/SPI_DO  |

| 6     | P3.2/INT0B/ADC10  | 15    | P1.3/PWMC/ADC3/T0      |

| 7     | P3.3/INT1B/ADC11  | 14    | P1.2/PWMB/ADC2/T1      |

| 8     | P3.4/PFD/ADC12    | 13    | P1.1/ T2EX/ADC1/CMPN   |

| 9     | P3.5/SPI_DI/ADC13 | 12    | P1.0/PWMA/T2/ADC0/CMPP |

| 10    | GND               | 11    | P3.7/SCL1/VREF/ ADC15  |

Table 1. MS89F/L series DIP/SOP20 Pins Configuration.

**Pin Descriptions**

| DIP20<br>Pin<br>No. | Notation                   | Ι/Ο | Functional Description                                                                       |

|---------------------|----------------------------|-----|----------------------------------------------------------------------------------------------|

| 1                   | RESETB/P3.6/ADC14          | I/O | P3.6 or RESETB to reset MS89F/L<br>SERIES to a known state.                                  |

| 2                   | P3.0/RXD                   | I/O | P3.0 or UART RXD function.                                                                   |

| 3                   | P3.1/TXD                   | I/O | P3.1 or UART TXD function.                                                                   |

| 4                   | XTAL2/P0.1/ADC9            | I/O | Oscillator pin or P01.                                                                       |

| 5                   | XTAL1/P0.0/ADC8            | I/O | Oscillator pin or P00. If ERC is used, this pin should connect to a resistor.                |

| 6                   | P3.2/INT0B/ADC10           | I/O | P3.2 or INT0B                                                                                |

| 7                   | P3.3/INT1B/ADC11           | I/O | P3.3 or INT1B                                                                                |

| 8                   | P3.4/PFD/ADC12             | I/O | P3.4 or PFD(Programmable frequency output)                                                   |

| 9                   | P3.5/SPI_DI/ADC13          | I/O | P3.5 or SPI_DI (SPI data input from external device)                                         |

| 10                  | GND                        | PWR | Ground for digital circuits.                                                                 |

| 11                  | P3.7/SCL1/VREF/ADC1<br>5   | I/O | P3.7, I2C Port 0 clock, or analog VREF.                                                      |

| 12                  | P1.0/PWMA/T2/ADC0/C<br>MPP | I/O | P1.0, PWM channel A, T2 pin, ADC<br>channel 0 input, or analog comparator<br>Positive input. |

| 13                  | P1.1/<br>T2EX/ADC1/CMPN    | I/O | P1.1, T2EX pin, or ADC channel 1, or analog comparator negative input.                       |

| 14                  | P1.2/PWM2/ADC2/T1          | 1/0 | P1.2, PWM channel B, or ADC channel 2, or T1.                                                |

| 15                  | P1.3/PWM3/ADC3/T0          | I/O | P1.3, PWM channel C, or ADC channel 3, or T0.                                                |

| 16 | P1.4/SDA2/ADC4/SPI_D<br>DI | 1/0 | P1.4, I2C port 2 data I/O, or SPI data to external device, or ADC channel 4. |

|----|----------------------------|-----|------------------------------------------------------------------------------|

| 17 | P1.5/SCL2/ADC5/SPI_C<br>LK | I/O | P1.5, I2C port 2 clock, or SPI clock to/from external device.                |

| 18 | P1.6/ADC6                  | I/O | P1.6 or ADC channel 6.                                                       |

| 19 | P1.7/SDA1/ADC7             | I/O | P1.7 or I2C port 0 data I/O.                                                 |

| 20 | VDD                        | VDD | Digital VDD.                                                                 |

Table 2. MS89F/L SERIES Pins Description.

### Absolute Maximum Ratings

#### Comments

MS89FXX DC Supply Voltage ....-0.5V to + 5.5 V MS89LXX DC Supply Voltage ....-0.5V to + 4.0 V Input Voltage.....-0.5V to VDD + 0.5V Output Voltage.....-0.5V to VDD + 0.5V Operating Temperature.....-40° to 85° C Storage Temperature......-70° to 150° C Never allow a stress to exceed the values listed under "Absolute Maximum Ratings", otherwise the device would suffer from a permanent damage. Nor is a stress at the listed value be allowed to persist over a period, since an extended exposure to the absolute maximum rating condition may also affect the reliability of the device, if not causing a damage thereof.

### 8052 Compatible CPU Core

MS81/89 Series uses 8052 compatible CPU Core. The CPU has the following features:

- 1. Harvard Machine, 8-bit<sup>2</sup> Data memory and 8-bit Program accessed at the same time, cause it the fastest general-purpose 8-bit CPU for complex controller applications.

- 2. CISC CPU, complex instruction set and bit-addressing mode may reduce program code size to the smallest. The features are listed below:

a) Memory-mapped register bank. Each bank has 8 registers and totally 4 banks can be selected. Mapped registers can do most calculation and use the least number of code memory.

b) Optimized Accumulator and memory-mapped register bank data movement. Only 1 byte instruction may move the data to/from the register and the accumulator.

b) Bit-addressing mode, set/clear/toggle a bit of bit-addressable I/O register needs only 2 bytes.

c) Optimized 2K subroutine call and branch, 2 bytes of program code can branch to another address in 2K bytes.

- e) Optimized "Decrease" and "branch if zero" into single byte instruction.

- f) Optimized "Compare" and "jump if not equal" into single byte instruction.

- g) 8-bit Multiplication and Division instruction supported.

- h) High-low 4-bit nimble operations supported.

- i) 3 bytes instruction to move data in non-register memory.

- j) Logic operation may be applied to mapped SFR directly.

- 3. Standard I/O, UART, Timers, Interrupt, and Event counters, make the application program portable between most 8051 compatible applications.

- 4. MSHINE 8051 core do lots of the instructions in 1 or 2 cycles, and is one of the fastest 8051 CPU on the market.

Comparing to other 8-bit CPU, especially VON-NEWMAN machines, the 8051 core will have worse performance only at 16-bit data addressing space. Since 8051 always need to use indirect addressing mode for 16-bit addressable data, it takes more cycles to do large data operations, or C/X/P memory operations. The following sub-sections will introduce the internals of the MSHINE 8051 CPU in more details.

for P/X memory may be extend to 16-bit wide.

<sup>&</sup>lt;sup>2</sup> Data bus width is 8-bit. Address bus width can be modified. Address bus for IRAM is fixed to 8 bit. Address bus

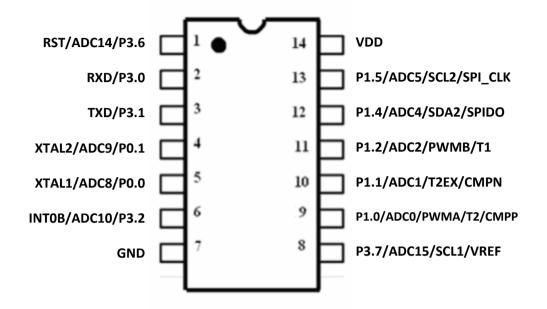

### **CPU** Architecture

MSHINE 8052 CPU core has the following structure.

Figure 3. MSHINE 8051 Core structure.

It is shown that code memory is independent from register bank and registers, pipelined instruction execution make it possible to run an instruction per cycle.

### Memory Types

Usually a standard 8052 CPU core may have the following memories connected:

- SFR & direct accessing RAM. This area has 256 bytes of addressing space. However, it is usually divided into 2 parts. Low part direct accessing SRAM have 128 bytes, and high 128 bytes are for special function registers (SFR). In the low addresses, the first 32 bytes may be switch to register banks. Each bank has 8 bytes, named R0-R7, selected by PSW register bits. R0-R7 registers are used in Implied Addressing Mode instructions.

- 2. Bit Addressable Memory. Direct addressable addresses (RAM and SFR) 0x00, 0x08, 0x10, 0x18,...0xf8 with C flag are bit addressable.

- Indirect RAM (IRAM) and STACK memory. IRAM and STACK may access up to 256 bytes of RAM, from 0x00~0xFF. While CPU using direct-addressing mode address 0x80~0xFF to access SFR, RAM at 0x80~0xFF may be used by STACK or indirect addressing mode like MOV A,@R0 instructions.

- 4. Code memory. 8052 CPU may "read" the code memory with special addressing mode. It cannot modify it directly since it uses FLASH on MS81/MS89 Series.

- 5. P-Memory and X-Memory. Formerly X-memory means the "External" memory of 8052. However, since the memory is "on-chip" with MS81/MS89 Series, "External" memory will cause confusing. Here it is called on-chip "X-memory" instead, and it just means the addressing space accessing with DPTR register with MOVX instructions. For different compilers, there is another "P" Memory for addressing. P-memory means the addressing space accessing with R0 and R1 registers with MOVX instructions, and P2 as the high address byte. MSHINE 8052 core mapped these memory spaces to the same address space. CPU

may use DPTR to access RAM from 0000~00FF and uses R0/P2 to access FF00~FFFF, or vice-versa.

### 8052 Compatible Special Function Registers (SFR)

Standard 8052 CPU has the following SFR that is compatible among them.

#### I/O Registers

Standard 8052 CPU may access to P0, P1, P2, and P3 at fixed address. Please see I/O ports at later sections.

#### Register Banks

Direct Accessed RAM 00~1F may be divided into 4 register banks. Each bank has registers R0~R7 that can be used for implied addressing mode instructions. Bank selection is by <RS1,RS0> of PSW register.

#### Accumulator (ACC)

ACC register is used for arithmatic operations, like addition, substraction, and logic operations.

#### Program Status Word (PSW)

PSW register has "Carry", "Overflow", "Parity", and "Carry for low 4-bit" are available. Also <RS1,RS0> flags are used to select register bank.

#### Program Counter (PC)

The 16-bit program counter means the Code memory address that the CPU is executing. It always increases 1 except the following conditions:

- 1. Branch.

- 2. Interrupt.

- 3. Longer execution cycles like MUL (multiplication), etc.

#### Stack Pointer (SP)

The 8-bit SP register points to the IRAM and it will "increase 2" when CPU enters a function call or interrupt service routine, because CPU will save 2 bytes of (next) program counter to the stack. And CPU will pop the program counter from the stack after the routine is end by RET or RETI instruction.

#### Data Pointer (DPTR)

The 16-bit DPTR register is used for accessing X-memory and C memory that needs 16-bits address bus. It may be seperate as DPL/DPH as 8-bit registers.

#### Interrupt Registers

The IE register is used for interrupt "ENABLE" control and IP register is for priority control. Totally 2 priorities can be set for different events.

#### **Timer Registers**

Timer 0,1, and 2 are standard timers, corresponding registers are TCON, TMOD, T2CON, RCAP2H/L, TH0, TL0, TH1, TL1, TH2, and TL2.

#### Serial Control Registers

SCON register used for SERIAL communication. See "Serial Communication" at later sections.

#### **B** Register

B register is used for multiplication and division.

#### PCON Register

Power down mode and IDLE mode are standard operating mode for 8052 compatible CPU. See "power control modes" at later sections.

#### Non-compatible Functions and Registers

MS81/MS89 Series thus have the following non-compatible functions/SFR to standard 8052 CPU.

- a) TDIV register. Formerly 8052 a cycle needs 12 clocks.

- b) PCON register bits 4,5. MS89 Series may use different clock for power saving.

- c) ADC related functions and registers. Standard 8052 has no ADC function.

- d) PWM, PFD, SPI, I2C, EFLASH, Watchdog Timer related functions and registers. Formerly 8052 has none of these functions.

#### Standard 8052 Addressing Modes

The standard 8052 has the following addressing mode that are also used in MS89 and MS81 Series.

#### Implied Register Addressing Mode

The implied addressing mode is fast and usually needs only 1 bytes. It include the following instructions:

- a) MOV instruction with ACC and R0~7 as operands.

- b) ADD/ADDC/SUBB/ANL/ORL/XRL/DEC with ACC and R0~R7 as operands.

- c) INC with ACC and R0 $\sim$ R7, or DPTR as operands.

- d) Rotate and shift (RR/RL/RRC/RLC) instructions with ACC as its operands.

- e) CPL (complementory) and CLR with ACC/Carry flag as its operands.

- f) MUL and DIV instructions.

- g) DJNZ with R0~R7, ACC as its operands.

The implied instruction usually is very fast executed and saves a lot of program memory.

#### Bit Addressing Mode

There are 256 bits of RAM/SFR can be direct accessed by CPU, with the following instructions:

- a) SETB, set a bit.

- b) CLR, clear a bit.

- c) CPL, complement a bit.

- d) "MOV <bit-address>,C" or "MOV C,<bit-address>"

The bit-addressable area has 2 region, first is memory from 20~3F, which maps to bit address 00-7F, and the other is SFR  $80,88,90,98\cdots$ F8.

Bit-addressing mode has following benefit comparing to normal parallel addressing modes:

- a) Save time and speed. If no bit-addressing mode, CPU should READ a byte, AND/OR a byte, and then WRITE it back for the same function.

- b) CPU and Hardware can set/clear the same bit. The above READ/AND-OR/WRITE will have a risk that some other bits may be toggled by hardware after READ but before WRITE. If no bit-addressing mode is provided, those bits can only be "READ-ONLY", which means CPU may NOT write to those bits to prevent hardware toggled bits modified by software. Bit addressing mode make the CPU has the ability to toggle the bits that can be set or cleared also by hardware. That is, some hardware interrupt can also be triggered by CPU itself, also named "fake" interrupts. It is not possible if no bit-addressing mode.

#### Immediate Addressing Mode

All the registers, IRAM and SFR may store "constant" to it. All constants are known as Immediate Addressing Mode.

#### Direct Addressing Mode

The "Direct Addressing Mode" can access all SFR at address 0x80~0xFF, while accessing RAM at 0x00~7F. All the movement, arithmetic, and stack operations support this addressing mode. The instructions include MOV, ADD, ADDC, SUBB, ORL, ANL, XRL, PUSH, POP.

#### Indexed (Indirect) Addressing Mode

Indexed addressing mode may access 3 kinds memories:

- a) IRAM, using R0, R1 as index, with MOV A,@R0 instruction, or ADC A,@R0.

- b) P-Memory, also R0, R1 as index, with instructions like MOVX A,@R0 instruction. Note that P2 will be used for high byte address for P-Memory. Here it is also the X-Memory.

- c) X-Memory, with DPTR as 16-bit index, uses the instruction like MOV A,@DPTR.

- d) Code Memory, with DPTR/PC as base, ACC as index. MOV A, @A+DPTR

#### MSHINE 8052 Instruction Execution

MSHINE 8052 executes the instructions most in 2 clock cycles, since most instructions have 2 bytes. Because it is Harvard machine, operation result write-back is overlapped with first instruction fetch cycle. The exception is when CPU is running at X-Memory. Because it becomes "VON-NEWMAN" machine when CPU runs X-RAM.

Some 1-byte instructions like "SETB C", may be pipelined to 1 clock cycle, that is what "1-T" means.

MSHINE 8052 CPU needs more cycles to read X and P memory. For details, please contact MSHINE Technologies Corp.

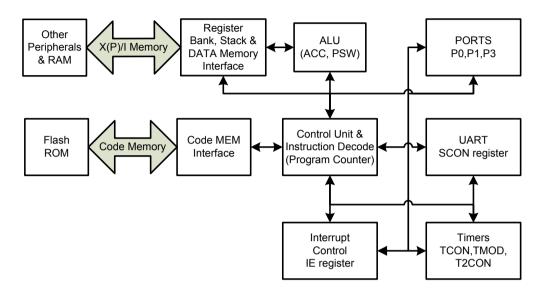

### MS81/MS89 Series Memory Map

MS89F/L SERIES has 256 bytes XMEM that can be switched to Program memory 0x0000~0x00FF. Total 512 bytes of RAM and 8192 bytes of ROM. Note that XMEM SFR and SRAM may be accessed by instructions like "MOVX A,@R0", with P2 set to 0x00 or 0xff.

Figure 4. Memory Map.

### SFR Registers

Special Function registers are listed in the following tables. Detailed descriptions are in later chapters.

| Part A, Direct Addressing | Mode SFR registers. |

|---------------------------|---------------------|

|---------------------------|---------------------|

| HIGH/LOW<br>ADDRESS | 0 (BIT<br>ADDRESSABLE) | 1      | 2      | 3      | 4      | 5      | 6      | 7      |

|---------------------|------------------------|--------|--------|--------|--------|--------|--------|--------|

| 80H                 | P0                     | SP     | DPL    | DPH    |        |        |        | PCON   |

| 88H                 | TCON                   | TMOD   | TL0    | TL1    | TH0    | TH1    |        |        |

| 90H                 | P1                     |        |        |        |        |        |        |        |

| 98H                 | SCON                   | SBUF   |        |        |        |        |        |        |

| A0H                 |                        |        |        |        |        |        |        |        |

| A8H                 | IE                     |        |        |        |        |        |        |        |

| B0H                 | P3                     |        |        |        |        |        |        |        |

| B8H                 | IP                     | PFDRLD | PWH    | RCCTL  | XTLCTL | TOPT   |        | PWCNTH |

| COH                 | SYSC                   | SYSC2  | PWTH   | PWPH   | PWPL   | PWEN   | PWCON  | PWCNT  |

| C8H                 | T2CON                  |        | RCAP2L | RCAP2H | TL2    | TH2    | ADH    | ADL    |

| D0H                 | PSW                    |        | PODIR  | P1DIR  |        | P3DIR  | TDIV   |        |

| D8H                 | ADCON                  |        | ADCSRC |        | ANAIO1 | ANAIO2 | ADCREF | CMPCON |

| E0H                 | ACC                    |        |        |        |        |        |        |        |

| E8H                 | LVDR                   |        |        |        |        |        |        |        |

| FOH                 | В                      |        |        |        |        |        |        |        |

Part B. XMEM Addressing Mode.

| HIGH/LOW | 0         | 1       | 2      | 3       | 4       | 5       | 6       | 7       |

|----------|-----------|---------|--------|---------|---------|---------|---------|---------|

| ADDRESS  |           |         |        |         |         |         |         |         |

| FF00H    | XMEMCON   | DEVID   |        |         |         |         |         |         |

| FF08H    | SPIINT    | SPICON  | SPIDAT |         |         |         |         |         |

| FF10H    | I2C0INT   | I2C0CON | I2C0DA | I2C0DIV | I2C1INT | I2C1CON | I2C1DAT | I2C1DIV |

|          |           |         | Т      |         |         |         |         |         |

| FF18H    |           |         |        |         |         |         |         |         |

| FF20H    | EFLASHCON | PRGAL   | PRGAH  | PRGDAT  |         |         |         |         |

| FF28H    |           |         |        |         |         |         |         |         |

| FF30H    |           |         |        |         |         |         |         |         |

| FF38H    |           |         |        |         |         |         |         |         |

#### Direct Addressing Mode registers

| Address | Notation | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Default value |

|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 80H     | P0       | Port 0 control register note that only 2 bits are accessible                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 00H           |

|         |          | here.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |

| 81H     | SP       | Stack pointer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 81H           |

| 82H     | DPL      | Data pointer Lower address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 00H           |

| 83H     | DPH      | Data pointer High address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 00H           |

| 87H     | PCON     | Power Control Register<br>Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0<br>SMO - CK1 CK0 GF1 GF0 PD IDL<br>D<br>Bit 7: SMOD, set 1 for double baud-rate.<br>Bit <5, 4>: <ck1, ck0="">, set for CPU clock rate. Note<br/>default values of these 2 bits are also OTP Programmable.<br/>R/W of these 2 bits is available.<br/>=&lt;0, 0&gt; select CPUCLK=system clock (RC or OSC)<br/>=&lt;0, 1&gt; select CPUCLK=system clock (RC or OSC) /2<br/>=&lt;1, 0&gt; select CPUCLK=system clock (RC or OSC) /4<br/>=&lt;1, 1&gt; select CPUCLK=system clock (RC or OSC) /8<br/>Note that CPUCLK is the only clock source of CPU, and the<br/>clock will give to timers, too.</ck1,> | 0-NN0000 B    |

|         |          | Bit 3: GF1, General bit addressable bit.<br>Bit 2: GF0, General bit addressable bit.<br>Bit 1: PD, Power down this chip by setting this bit to 1.<br>Bit 0: IDL. Set this bit to 1 to enter idle mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |

| 88H     | TCON     | Timer Control register,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 00H           |

|     |      | Bit 7<br>TF1                                                                                                                                                                                                                            | Bit 6<br>TR1                                                                                                                                                                                                                                              | Bit 5<br>TF0                                                                                                                                                                                                              | Bit 4<br>TR0                                                                                                                                                                                                            | Bit 3<br>IE1                                                                                                                                                                                                         | Bit 2<br>IT1                                                                                                                                                                | Bit 1<br>IE0                                                                                                                                                 | Bit 0<br>IT0                                                                                                                                                                                 |     |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     |      | timer 1<br>interrup<br>Bit 6: T<br>enable<br>Bit 5:<br>timer 1<br>interrup<br>Bit 4: T<br>enable<br>Bit 3: I<br>when I<br>with RE<br>be set<br>CPU m<br>Bit 2: T<br>EDGE<br>Bit 1: I<br>externa<br>low. C<br>routine<br>cause<br>Bit 0: | overflo<br>ot routin<br>R1, Tin<br>/disable<br>TF0, Tin<br>overflo<br>ot routin<br>R0, Tin<br>/disable<br>E1, Ext<br>E1, Ext<br>E1, Ext<br>E1, Ext<br>E1, in co<br>by CPU<br>anually<br>T1, inte<br>interrup<br>E0, Ext<br>a interru<br>leared k<br>autom | w, and<br>e autoiner 1 R<br>e the tir<br>mer 0<br>w, and<br>e autoiner 0 R<br>e the tir<br>ernal I<br>3) inte<br>rrespo<br>J to ca<br>rrupt 1<br>t.<br>ernal in<br>upt (IN<br>by hard<br>atically<br>e interr<br>errupt ( | I cleared<br>matically<br>un contr<br>ner/cour<br>d cleared<br>matically<br>un contr<br>ner/cour<br>nterrupt<br>errupt ha<br>nding se<br>use sof<br>control.<br>nterrupt<br>TOB, P3<br>lware as<br>. Also, f<br>upt and | l by hai<br>/.<br>ol bit, sinter 1.<br>/ flag.<br>l by ha<br>/.<br>ol bit, sinter 1.<br>1 Flag<br>uppens<br>rvice root<br>tware in<br>Set this<br>0 flag.<br>.2) sou<br>it enter<br>this bit<br>clear it<br>I bit (F | rdware v<br>set/clea<br>Set by<br>rdware v<br>set/clea<br>. Set al<br>. Cleare<br>outine. A<br>nterrupt<br>s bit 1 t<br>Set by<br>urce goo<br>ers the i<br>can be<br>by CPL | when le<br>r by so<br>hardwa<br>when en<br>r by so<br>r by so<br>so by h<br>and cl<br>and cl<br>co enab<br>hardwa<br>es from<br>nterrup<br>set by<br>J manua | are when<br>aves the<br>ftware to<br>are when<br>nters the<br>ftware to<br>nardware<br>s bit can<br>ear it by<br>le INT1B<br>are when<br>high to<br>t service<br>CPU to<br>ally.<br>bit 1 to |     |

| 89H | TMOD |                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                           |                                                                                                                                                                                                                         |                                                                                                                                                                                                                      |                                                                                                                                                                             |                                                                                                                                                              |                                                                                                                                                                                              | 00H |

|     |      | Bit 7<br>Timer 1<br>GATE<br>High 4<br>used to<br>Bit 7, 4<br>Timer/4<br>GATE=<br>Bit 6,3<br>by soft<br>operati<br>Bit <5,<br><m1, m<br="">&lt;0, 0&gt;<br/>&lt;0, 1&gt;<br/>&lt;1, 0&gt;<br/>&lt;1, 1&gt;<br/>standa</m1,>              | Bit 6<br>control<br>C/TB<br>bits are<br>bits are<br>control<br>GATE<br>Counter<br>0, Time<br>C/TB,<br>ware fo<br>on.<br>4>/<1,(<br>MO>=<br>: 13 bit<br>: 8 bit a<br>: TL0<br>rd timer                                                                     | Bit 5<br>M1<br>e used<br>l timer<br>, Wher<br>1/0 wil<br>er/Cour<br>Timer<br>r timer<br>c)>: M1<br>timer/c<br>timer/c<br>uto-re<br>is an 2<br>0 con                                                                       | 0<br>n TR1/0<br>I run onl<br>nter1/0 w<br>or count<br>operatic<br>,M0, Op<br>counter.<br>counter.<br>load tim<br>3-bit tin                                                                                              | Bit 3<br>Timer (<br>GATE<br>rol Tim<br>is 1 an<br>y when<br>yill run<br>er sele<br>on, and<br>eration<br>(8048<br>er/cour<br>rer/cour<br>TH0 is a                                                                    | Bit 2<br>C/TB<br>er1, and<br>d GATE<br>INTx is<br>only who<br>ctor. Th<br>set 1 fo<br>modes<br>compat<br>nter.<br>inter co<br>another                                       | =1,<br>high. V<br>en TR1/<br>is bit is<br>or event<br>, listed<br>ible)<br>ontrollec<br>timer co                                                             | /0=1.<br>cleared<br>counter                                                                                                                                                                  |     |

| 8AH  | TL0   | Timer/Counter 0 low byte                                                   | 00H        |

|------|-------|----------------------------------------------------------------------------|------------|

| 8BH  | TL1   | Timer/Counter 1 low byte                                                   | 00H        |

| 8CH  | TH0   | Timer/Counter 0 high byte                                                  | 00H        |

| 8DH  | TH1   | Timer/Counter 1 high byte                                                  | 00H        |

| 90H  | P1    | Port 1 control bits.                                                       | FFH        |

| 98H  | SCON  | Serial Port control register,                                              | 00H        |

| 0011 | 00011 |                                                                            | 0011       |

|      |       | Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0                            |            |

|      |       | SMO SM1 SM2 REN TB8 RB8 TI RI                                              |            |

|      |       |                                                                            |            |

|      |       |                                                                            |            |

|      |       | Bit <7,6>: SM0, SM1, Serial port mode control,                             |            |

|      |       | =<0,0>, Mode 0, serial port is used as shift register, clock is            |            |

|      |       | FOSC/12                                                                    |            |

|      |       | =<0,1>, Mode 1, serial port is used as 8-bit UART, clock is                |            |

|      |       | variable.                                                                  |            |

|      |       | =<1,0>, Mode 2, serial port is used as 9-bit UART, clock is                |            |

|      |       | Fosc/64 or Fosc/32.                                                        |            |

|      |       | =<1,1>, Mode 3, serial port is used as 9-bit UART, clock is                |            |

|      |       | variable.                                                                  |            |

|      |       | Bit 5: SM2, Enable the multiprocessor communication                        |            |

|      |       | feature in Mode 2 and 3. In Mode 0, this bit should set to 0.              |            |

|      |       | In mode 1, SM2=1 let RI is activated only when stop bit is                 |            |

|      |       | received. In Mode 2 and 3, SM2=1 let RI is activated only                  |            |

|      |       | when the 9 <sup>th</sup> bit is 0.                                         |            |

|      |       | Bit 4: REN, set/clear by software to enable/disable the serial             |            |

|      |       | data receiving.                                                            |            |

|      |       | Bit 3: TB8, the 9 <sup>th</sup> bit value that will be send in mode 2 and  |            |

|      |       | 3.                                                                         |            |

|      |       | Bit 2: RB8, the 9 <sup>th</sup> bit value of mode 2 and 3. In mode 1, this |            |

|      |       | bit will be the received stop bit if SM2=0. In Mode 0, RB8 is              |            |

|      |       | not used.                                                                  |            |

|      |       | Bit 1: TI, Transmit interrupt flag, this bit will be set by                |            |

|      |       | hardware at the end of 8 <sup>th</sup> bit time in mode 0. Or at the       |            |

|      |       | beginning of the stop bit of other modes. This bit must be                 |            |

|      |       | cleared by software.                                                       |            |

|      |       | Bit 0: RI, Receive interrupt flag, This bit will be set by                 |            |

|      |       | hardware at the end of 8 <sup>th</sup> bit time at Mode 0, or half way     |            |

|      |       | through the stop bit time in other modes. (Except see SM2)                 |            |

|      |       | This bit must be cleared by software.                                      |            |

| 99H  | SBUF  | Serial Port buffer, read this byte for data received, write this           | XXXXXXXX B |

|      |       | byte to transmit data.                                                     |            |

| A0   | P2    | Used for PMEM accessing. P2=0x00 will access SRAM of                       | OFFH       |

|      |       | XMEM, and P2=0xff will access SFR of XMEM.                                 |            |

| A8H  | IE    | Interrupt enable register.                                                 | 00H        |

|      |       |                                                                            |            |

|      |       | Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0EAADCET2ESET1EX1ET0EX0             |            |

|      |       |                                                                            |            |

|      |       |                                                                            |            |

|      |       | Bit 7: EA, all interrupts are disabled if this bit is 0.                   |            |

|      |       | ,                                                                          |            |

|         |        | Bit 6: ADC, Enable or disable ADC interrupt.                     |            |

|---------|--------|------------------------------------------------------------------|------------|

|         |        | Bit 5: ET2, Enable timer 2 interrupt if this bit set to 1.       |            |

|         |        | Bit 4: ES, Enable or disable serial port interrupt.              |            |

|         |        | Bit 3: ET1, Enable or disable timer 1 overflow interrupt.        |            |

|         |        | Bit 2: EX1, Enable or disable P3.3 (INT1) interrupt.             |            |

|         |        | Bit 1: ET0, Enable or disable timer 0 overflow interrupt.        |            |

|         |        | Bit 0: EX0, Enable or disable P3.2 (INT0) interrupt.             |            |

| B0H     | P3     | Port 3 control register                                          | 00H        |

| B8H     | IP     | Interrupt Priority register, 0 is lower priority and 1 is higher | 00 0000 B  |

| DOLL    | 11     | priority.                                                        | 00 0000 D  |

|         |        | pronty.                                                          |            |

|         |        | Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0                  |            |

|         |        | PADC PT2 PS PT1 PX1 PT0 PX0                                      |            |

|         |        |                                                                  |            |

|         |        | Bit 6: PADC, ADC interrupt priority level.                       |            |

|         |        |                                                                  |            |

|         |        | Bit 5: PT2, Timer 2 priority bit.                                |            |

|         |        | Bit 4: PS, Serial Port priority level.                           |            |

|         |        | Bit 3: PT1, Timer 1 priority level.                              |            |

|         |        | Bit 2: PX1, external INT1B interrupt priority level.             |            |

|         |        | Bit 1: PT0, Timer 0 interrupt priority level.                    |            |

|         |        | Bit 0: PX0, external INT0B interrupt priority level.             |            |

| B9H     | PFDRLD | PFD period reload register                                       | XX         |

|         |        | This register will load to a 8-bit counter, which make PFD       |            |

|         |        | toggle when that counter overflows.                              |            |

| BAH     | PWH    | MSB settings of PWM channel n                                    | 0000 0000B |

| D/ (III |        | Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0                  | 0000 00000 |

|         |        | PWL1 PWL0 PWT9 PWT8                                              |            |

|         |        |                                                                  |            |

|         |        | Bit<7,6>: <pwl1,0> PWM Channel N resolution selection</pwl1,0>   |            |

|         |        | <0, 0> PWM has 7-bit resolution                                  |            |

|         |        | <0, 1> PWM has 8-bit resolution                                  |            |

|         |        | <1, $0$ PWM has 9-bit resolution                                 |            |

|         |        | <1, 1> PWM has 10-bit resolution                                 |            |

|         |        |                                                                  |            |

|         |        |                                                                  |            |

|         |        |                                                                  |            |

|         |        | Bit <1, 0>: <pwt9,8>, PWM Duty threshold value setting,</pwt9,8> |            |

|         |        | MSB. LSB is set/read from PWTH Register.                         |            |

|         |        |                                                                  |            |

|         |        |                                                                  |            |

| BBH     | RCCTL  | RC oscillator control register                                   | 000nnnnn   |

|         |        | Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0                  |            |

|         |        | RCOE ERCEN IRCEN OSCF[4:0]                                       |            |

|         |        |                                                                  |            |

|         |        | This register is mainly for test mode:                           |            |

|         |        | Bit <7>: RCOE, output RC clock to P3.7                           |            |

|         |        | Bit <6>: ERCEN. When test mode, this bit set to 1 may            |            |

|         |        | enable External RC.                                              |            |

|         |        | Bit <5>: IRCEN. When using external RC, this bit set 1 may       |            |

|         |        | enable                                                           |            |

|         |        |                                                                  |            |

| 1       |        | Bit <4:0>: OSCF. IRC frequency may be re-tuned by this           |            |

|         |        |                                                                  |            |

|         |        | register.                                                        |            |

| BCH | OSCCTL | Crystal Oscillator Control register<br>Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0<br>WDTE XTLO XTLE<br>N E N<br>Bit<4>, WDTEN, enable watchdog manually by setting this<br>bit to 1.<br>Bit<1>, XTLOE. Output XTL clock to P3.7<br>Bit<0>, XTLEN. When using IRC, enable this bit may enable<br>XTL connected.                                                                                                                                                                                   | 0 <b></b> 00B |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| BDH | TOPT   | Testing Option RegisterBit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0LVSELVDEWDTEWDTCK_SEL[2:0]NNNThis register is for testing purpose. When the option is not correctly write, the register may force the code to WDT or LVDR by corresponding bits.                                                                                                                                                                                                                                                       | 0000000       |

| BFH | PWCNTH | PWM Counter High ByteBit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0PWCN PWCN<br>T9T8PWM Counter value, of the channel specified by PWEN.                                                                                                                                                                                                                                                                                                                                                                    |               |

| СОН | SYSC   | System Control Register, mainly for the special functions.Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0PCCPBCADCEPACPFDCPFDCPFDCBit 0:PFDE, set 1 to enable PFD function.Bit <2,1>: PFDCK <1,0>, select PFD clock source from<0,0>: oscillator<0,1>: oscillator/2<1,0>: oscillator/4<1,1>: oscillator/8Bit 5: ADCE, set 1 to enable ADC function.Bit 3: PAC, set 1 change PWM channel A to CMP mode.Bit 6: PBC, set 1 change PWM channel B to CMP mode.Bit 7: PCC, set 1 change PWM channel C to CMP mode. | 00H           |

| C1H | SYSC2  | System control register 2, mainly for IO and PFDBit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0P3CMP1CMPOCMWTIEWTCLWTIFBit 0P3CMP1CMP0CMWTIEWTCLWTIFBit 0Bit 1:Watchdog interrupt flag.Bit 2:WTCLR, set this bit 1 will clear the watch-dog counter.Bit 3:WTIE, set this bit 1 will make watchdog in interrupt mode.                                                                                                                                                                                         | 0000-000B     |

|     |       | Bit 4: P0CM, set 0 for default 80C31 I/O structure, set 1 for<br>CMOS I/O structure on Port 0.<br>Bit 5: P1CM, set 0 for default 80C31 I/O structure, set 1 for<br>CMOS I/O structure on Port 2.<br>Bit 7: P3CM, set 0 for default 80C31 I/O structure, set 1 for<br>CMOS I/O structure on Port 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| C2H | PWTH  | PWM toggle value. MSB is PWH.bit <0><br>Note that PWEN will select which channel PWM is active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 00H |

| СЗН | PWMPH | PWM Period High Byte.<br>Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0<br>PWM PWM<br>P9 P8<br>This register can read/write the PWM period register high 2<br>bits of the channel specified by PWEN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0xH |

| C4H | PWMPL | PWM Period Low Byte<br>This register can read/write the period of PWM channel<br>specified by PWEN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ХХН |

| C5H | PWEN  | PWM enable control.Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0PWAPWAPWCEPWBE-PWAECT1CT0NNNNPWXEN set 1 enable PWM channel X .PWACT<1,0>:selectthechannelactiveforPWCNT,PWTH,PWH,PWMPH,PWHPL, and PWCNTH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ХОН |

| С6Н | PWCON | PWM Control registerBit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0PCINPBINVPAINVPCKBPCKBPCKAPCKAV1010Bit <1,0>: <pcka1, pcka0="">, select the clock source ofPWM channel A&lt;0, 0&gt;: Channel A uses clock from OSC&lt;0, 1&gt;: Channel A uses clock from OSC/2&lt;1, 0&gt;: Channel A uses clock from OSC/4&lt;1, 1&gt;: Channel A uses clock from OSC/8Bit &lt;3,2&gt;: <pckb1, pckb0="">, select the clock source ofPWM channel B and C.&lt;0, 0&gt;: Channel B,C uses clock from OSC/2&lt;1, 1&gt;: Channel B,C uses clock from OSC/2&lt;1, 1&gt;: Channel B,C uses clock from OSC/4&lt;1, 1&gt;: Channel B,C uses clock from OSC/8Bit &lt;7~4&gt;: P<x>INV, Set 1 to make the PWM output inverted. This is useful for Push-pull operation.</x></pckb1,></pcka1,> | 00H |

| C7H | PWCNT | PWM cou             | unter v      | alue setting   | . PWM channel n, MSB is PWH                                   | 00H |

|-----|-------|---------------------|--------------|----------------|---------------------------------------------------------------|-----|

|     |       |                     |              |                | ter is to also set the initial value of                       |     |

|     |       |                     |              | is register is |                                                               |     |

| C8H | T2CON | Bit                 | Bit 7<br>TF2 | Bit 6<br>EXF2  | Bit 5 Bit 4<br>RCLK TCLK                                      |     |

|     |       | Notation<br>Default | 0            | 0              | 0 0                                                           |     |

|     |       | Delauli             | 0            | 0              | 0 0                                                           |     |

|     |       |                     |              |                |                                                               |     |

|     |       | 5.                  | 5.           |                |                                                               |     |

|     |       | Bit<br>Notation     | Bit<br>EXEI  |                | Bit 1 Bit 0<br>C/T2B CP/RL2B                                  |     |

|     |       | Default             | 0            | 0              | 0 0                                                           |     |

|     |       |                     |              |                |                                                               |     |

|     |       |                     |              |                |                                                               |     |

|     |       | BI NA               | ME           | BIT            | DESCRIPTION                                                   |     |

|     |       | T                   |              | ADDRES         | DESCRIPTION                                                   |     |

|     |       |                     |              | S              |                                                               |     |

|     |       | 7 TF                | 2            | CFh            | Timer 2 Overflow. This bit is                                 |     |

|     |       |                     |              |                | set when T2 overflows.                                        |     |

|     |       |                     |              |                | When T2 interrupt is                                          |     |

|     |       |                     |              |                | enabled, this bit will cause                                  |     |

|     |       |                     |              |                | the interrupt to be                                           |     |

|     |       |                     |              |                | triggered. This bit will not<br>be set if either TCLK or      |     |

|     |       |                     |              |                | RCLK bits are set.                                            |     |

|     |       | 6 EX                | F2           | CEh            | Timer 2 External Flag. Set                                    |     |

|     |       |                     |              |                | by a reload or capture                                        |     |

|     |       |                     |              |                | caused by a 1-0 transition                                    |     |

|     |       |                     |              |                | on T2EX (P1.1), but only                                      |     |

|     |       |                     |              |                | when EXEN2 is set. When                                       |     |

|     |       |                     |              |                | T2 interrupt is enabled, this bit will cause the interrupt to |     |

|     |       |                     |              |                | be triggered.                                                 |     |

|     |       | 5 RC                | LK           | CDh            | Timer 2 Receive Clock.                                        |     |

|     |       | _                   |              |                | When this bit is set, Timer 2                                 |     |

|     |       |                     |              |                | will be used to determine                                     |     |

|     |       |                     |              |                | the serial port receive baud                                  |     |

|     |       |                     |              |                | rate. When clear, Timer 1                                     |     |

|     |       |                     | LK           | CCh            | will be used.<br>Timer 2 Receive Clock.                       |     |

|     |       | 4 TC                | LN           | CCh            | When this bit is set, Timer 2                                 |     |

|     |       |                     |              |                | will be used to determine                                     |     |

|     |       |                     |              |                | the serial port transmit                                      |     |

|     |       |                     |              |                | baud rate. When clear,                                        |     |

|     |       |                     |              |                | Timer 1 will be used.                                         |     |

|     |       | 3 EX                | EN2          | CBh            | Timer 2 External Enable.                                      |     |

|     |       |                     |              |                | When set, a $1-0$ transition                                  |     |

|     |       |                     |              |                | on T2EX (P1.1) will cause a                                   |     |

|     |       | 2 TR                | 2            | CAh            | capture or reload to occur.<br>Timer 2 Run. When set,         |     |

|     |       |                     | Ĺ            |                | THILE Z THUIT. WITHEIT SEL,                                   |     |

|            |            | timer 2 will be turned on.<br>Otherwise, it is turned off.<br>Timer 2 Counter/Interval<br>Timer. If clear, Timer 2 is<br>an interval counter. If set,<br>Timer 2 is incremented by<br>1–0 transition on T2 (P1.0).<br>CP/RL2 C8h<br>B<br>clear, auto reload occurs<br>on timer 2 overflow, or<br>T2EX 1–0 transition if<br>EXEN2 is set. If set, a<br>capture will occur on a 1–0<br>transition of T2EX if EXEN2<br>is set. |                                                                                          |                             |                          |                            |                    |                        |                                        |      |   |